Reconfigurable fir filter vhdl code. N is the filter order.

How To Implement Fir Filter In Vhdl Surf Vhdl

We need a logo for a company and graphic design for the website see the word file attached for more details we need a logo for a company and graphic design for the website see the word file attached for more details - fir vhdl engineering electronics matlab.

. Then transform it to create a FIR Filter System object with a highpass response Hhp. Filter Design HDL Coder generates synthesizable portable VHDL and Verilog code for implementing fixed-point filters designed with MATLAB on FPGAs or ASICs. Design guidelines for using dsp blocks altera.

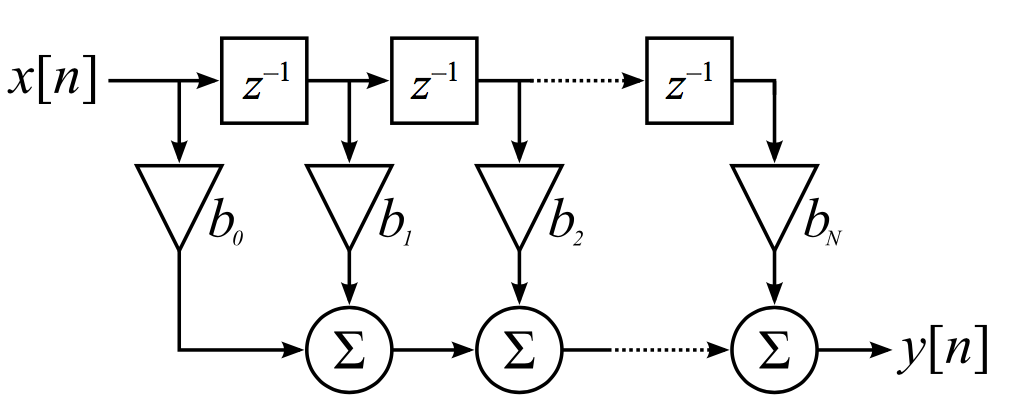

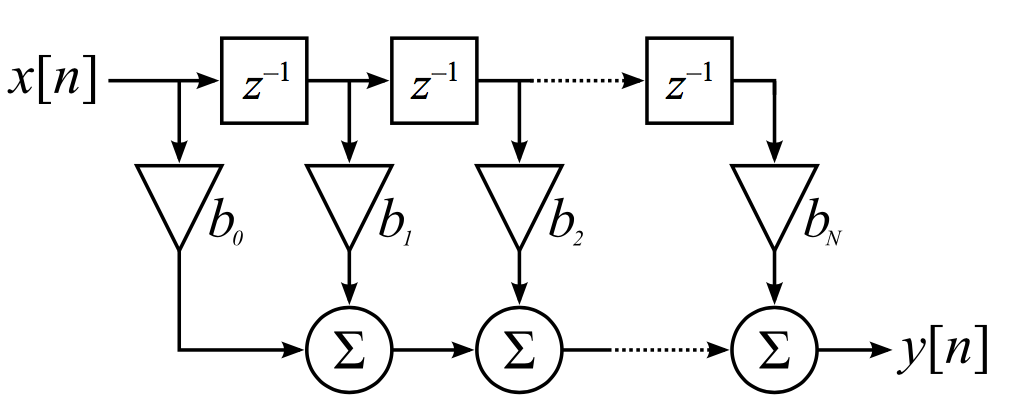

RTL-VHDL-Code Block diagram Algorithm High-Level System Diagram Context of the design Inputs and Outputs Throughputrates Algorithmic requirementsy k bi x k i N Algorithm Description Mathematical Description i 0 Performance Criteria x k y k. Digital filter design using vhdl. Well use a 32-tap FIR filter as an example.

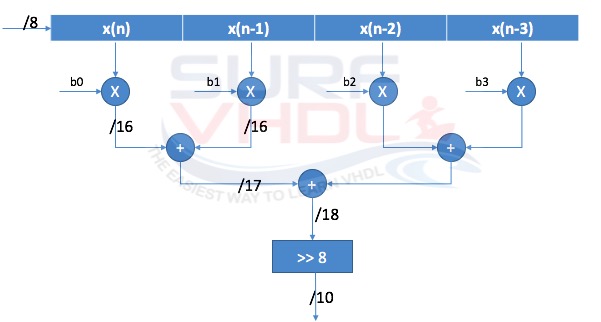

Sample ECG inputs are provided in inputtxt files the VHDL filter code reads those ECG files apply digital filtering and write the results into outputtxt files for verification. An implementation of a FIR filter in particular using the transposed form. This is a 4 tap filter.

Here y is the filter output x in the input signal and b is the filter coefficients. Mathematica electrical engineering matlab psd banner design. We will generate VHDL code for the filter and show the two responses using the generated VHDL test bench.

Free download here pdfsdocuments2 com. Very-high-speed integrated circuit is a hardware. Pipeline fir filters in verilog code design of 30 tap fir filter using vhdl ethesis.

Others will find that digital filter design and analysis is really not. VHDL VHSIC hardware description language. FIR Filter Design in Arria VCyclone V DSP Block Using VHDL Inferring.

Create the lowpass filter design object then create the FIR Filter System object Hlp. Timescale 1ns 1ps module FIRinput clk input reset input signed 150 s_axis_fir_tdata input 30 s_axis_fir_tkeep input s_axis_fir_tlast input s_axis_fir_tvalid input m_axis_fir_tready output reg m_axis_fir_tvalid output reg s_axis_fir_tready output reg m_axis_fir_tlast output reg 30 m_axis_fir_tkeep output reg signed 310. Video Lecture on an FPGA-Implementation of an FIR-Filter 2 of 4Project Homepagehttpwwwh-brsdefpga-vision-labSource Code available athttpsgithub.

The simplest low pass FIR filter you can try is y n x n x n-1. Generating clock-cycle-accurate FIR filter models also known as bit-true models in the Verilog HDL and VHDL languages and for the MATLAB environment M-files and Model Files. According to the formula you need the current and previous ADC samples in order to get the appropriate output.

FIR Filter Where to start. Hard built-in pre-adders can be used when implementing symmetric filters to. A design of generic fir filter is described in this work.

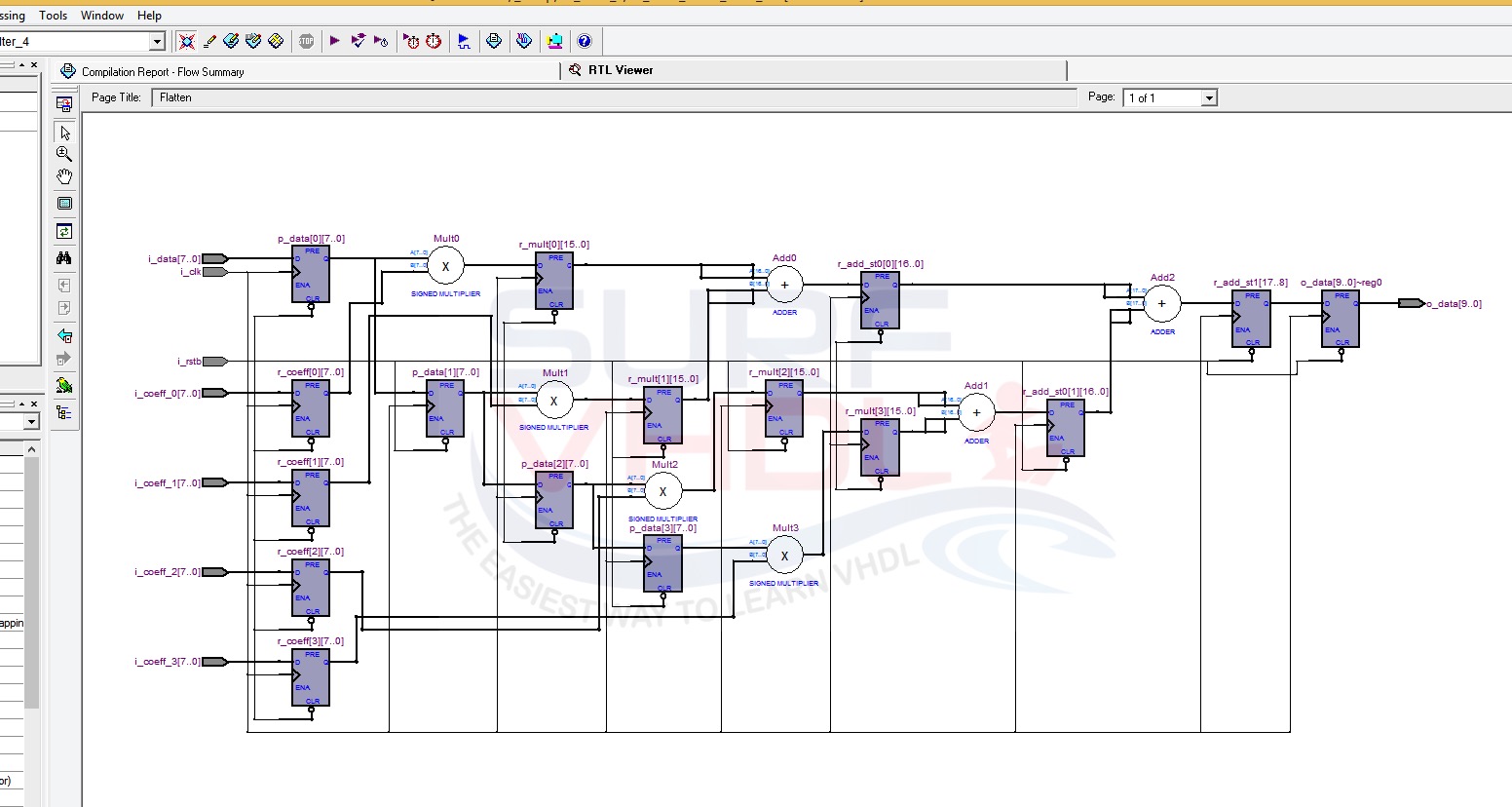

VHDL Coding for FIR Filter PPT Powerpoint The fir filter designed fully meets the design requirements. That means the order of the filter is 4 and so it has 4 coefficients. The VHDL code presented in this model will show you how to describe a typical reference model in VHDL.

The vhdl code of the filter test bench implements straight forward the architecture of figure 6. Finding the coefficients needed to design custom FIR filters. VHDL code for the FIR filter is fully presented.

March 31st 2018 - Design And Implementation Of A Digital Finite Impulse Response FIR Filter Algorithm In A FPGA The Created. Fpga Code example for FIR IIR filters in VHDL. 17 Design of FIR Filter Using Verilog HDL Copy Signal.

Run the testbench on ModelSim. Design of multiplier less 32 tap fir filter using vhdl. FIR module Verilog code.

You can say I have coded the exact block diagram available in the paper Figure 2. 1 Points Download Earn points. Modify the file VHDLfir_tbvhdl modifying the path for data io.

Transposed FIR Filter where N is the number of filter taps-1 ie. Check IOoutput_resultstxt for the result. For a discussion of the advantages of reference models please refer to our Tips page.

Figure 2 Transposed Form Of FIR Filter 09 Figure 3 Top level schema of the FIR filter 11 Figure 4 Xilinx 142 report of the filter design 13 Figure 5 VHDL Top level RTL Schema1 14 Figure 6 VHDL Top level RTL Schema2 14 Figure 7 Xilinx 142 full schematic of FIR order 30 filter. For writing the code in Verilog I have referred to the paper VHDL generation of optimized FIR filters. This is an fir filter implementation code for a reconfigurable fir filter design coded in vhdl language.

Coding tips and tricks VHDL code for a 4 tap FIR filter. Source Code reconfigurable fir filter vhdl code. In IOinput_vectorstxt put the input integer you want to test.

A finite impulse response FIR filter is a type of a discrete-time filter. Automatically generating the code required for the Quartus or MAXPLUS II software to synthesize high. The impulse response the filters response to a Kronecker delta input is finite because it settles to zero in a finite number of sample intervals.

Filter design is the process of designing a filter in the sense in which the term is used in signal processing statistics and applied mathematics often a linear shift-invariant filter which satisfies a set of requirements some of which are contradictory. It automatically creates VHDL and Verilog test benches for simulating testing and verifying the generated code. The higher the value of N is the more complex the filter will be.

The VHDL code for the FIR filter is simulated and verified by comparing the simulated results in Modelsim with the correct results generated from Matlab. 15 Figure 8 Test bench simulation of 30 order FIR filter 16. Below is a very simple block diagram of the hardware you want to implement.

For writing the code in VHDL I have referred to the paper VHDL generation of optimized FIR filters. We will generate vhdl code for the filter and show the two responses using the generated vhdl. Ee367 lab 6 creating a fir filter in vhdl.

Alteras 28-nm DSP architecture includes a host of features for optimizing FIR filter implementations. Finite Impulse Response FIR Filter. Vhdl code for fir filter - Digital Filters.

You can implement this quite easily in VHDL. Verilog Coefficients Reload. Letss look at some of the highlights of this model.

You can say I have coded the exact block diagram available.

How To Implement Fir Filter In Vhdl Surf Vhdl

How To Implement Fir Filter In Vhdl Surf Vhdl

4 Taps Fir Filter Iv Use Cases Download Scientific Diagram

Fpga Code Example For Fir Iir Filters In Vhdl Electrical Engineering Stack Exchange

Pdf Vhdl Generation Of Optimized Fir Filters Semantic Scholar

A Low Pass Fir Filter For Ecg Denoising In Vhdl Fpga4student Com

Fpga Fir Filter Circuit Architecture And Vhdl Design Youtube

A Low Pass Fir Filter For Ecg Denoising In Vhdl Fpga4student Com

0 comments

Post a Comment